## Diffusion studies of the Si $\delta$ -doped GaAs by capacitance-voltage measurement

T. H. Chiu, J. E. Cunningham, and B. Tell AT&T Bell Laboratories, Holmdel, New Jersey 07733

E. F. Schubert

AT&T Bell Laboratories, Murray Hill, New Jersey 07974

(Received 25 January 1988; accepted for publication 28 March 1988)

Using triethylgallium and arsine, high-quality GaAs can be grown at a relatively low substrate temperature of 500 °C by chemical beam epitaxy. Such a low temperature has the advantage of a negligible Si diffusion effect. Capacitance-voltage (C-V) measurements of the Si  $\delta$ -doped GaAs show extremely narrow profile widths of 22 Å at 300 K and 18 Å at 77 K, indicating a very high degree of Si spatial localization has been achieved. The subsequent annealing experiments reveal that significant Si segregation and diffusion exist at a high growth temperature of  $\sim 600$  °C, usually employed in conventional molecular-beam epitaxy. The C-V widths of the annealed  $\delta$ -doped structures also provide an excellent measure to determine the Si diffusion constant in GaAs.

Epitaxial growth of semiconductor structures employing narrow and intricate doping profiles normal to the surfaces is important for achieving high performance optoelectronic devices. In molecular-beam epitaxial (MBE) growth of GaAs, the  $\delta$ -doping technique employs growth interruption to allow the deposition of a two-dimensional (2D) layer of dopants embedded within one lattice constant along the growth orientation in the host crystal. This doping method gives ultimate control of the narrow doping profile. In the selectively doped AlGaAs heterostructure using Si, this  $\delta$ doping technique has led to significant enhancement in mobility and 2D electron concentration when compared to similar structures using homogeneous doping scheme. For high-quality GaAs the MBE growth temperature is relatively high (~600 °C) and the phenomena of Si diffusion and segregation in the growth front may not be negligible. This prevents the  $\delta$ -doping plane from being monolayer sharp. It was found necessary to use a low growth temperature of 520 °C (Ref. 2) to achieve narrow width of the capacitancevoltage (C-V) profile in the Si  $\delta$ -doped GaAs.

In chemical beam epitaxial (CBE) growth of GaAs the presence of mobile molecular Ga species modifies the growth kinetics in the growth front, which is supported by the studies using reflection high-energy electron diffraction (RHEED) during growth.3 Consequently, the optimal CBE growth conditions for GaAs may differ from conventional MBE. It has been shown recently that GaAs epilayers with excellent electrical and optical properties can be prepared using triethylgallium and arsine at a low growth temperature of 500 °C. In particular the carbon incorporation mechanism favors low growth temperature for lower carbon impurity concentration.<sup>4,5</sup> Furthermore, intrinsic to such low growth temperature is the advantage of much reduced impurity diffusion effect, important for preserving abrupt doping profile. In the present work we employ C-V profiling techniques on the  $\delta$ -doped structures to investigate Si diffusion in GaAs during the growth and its subsequent annealing behavior.

The  $\delta$ -doped structures were grown on Si-doped substrates. The undoped GaAs has a residual p-type background in the low  $10^{15}$ -cm<sup>-3</sup> range due to carbon. Si dopants were evaporated using effusion cell. The structures investigated generally consist of an undoped 1- $\mu$ m buffer layer, then single or multiple Si  $\delta$ -doped planes introduced by growth interruption to allow the deposition of Si up to some fraction of a monolayer. After the donor evaporation, a 0.1- $\mu$ m undoped cap layer was laid down, leaving the n-type Sidoping plane embedded in a slightly p-type epilayer. Details of the epitaxial growth of GaAs have previously been described. After the crystal growth, circular Ti/Au Schottky contacts were defined by evaporation through mask for electrical measurements.

Ideally, the Si dopants of the  $\delta$ -doped structure should be confined to one sublattice plane. The extent of Si localization is determined from the width of the C-V profile. In homogeneously doped layers, the resolution of the doping concentration determined from C-V measurements is known to be limited by the Debye screening length. The classical theory for C-V measurement may not strictly apply to the extremely narrow 2D degenerately doped quantum-mechanical system, and the spatial movement of the 2D electron gas wave functions under external bias voltage may need to be considered. Consequently the C-V profile may not be equal to the true impurity distribution of the  $\delta$ -doped structure. However, we show here the spatial location of the doping plane and the integrated donor concentration determined from the C-V measurement both correlate very well with the actual growth parameters. The annealing results discussed later in this paper also indicate that the full width at half maximum (FWHM) of the C-V profile remains a good approximation to estimate the extent of impurity localization.

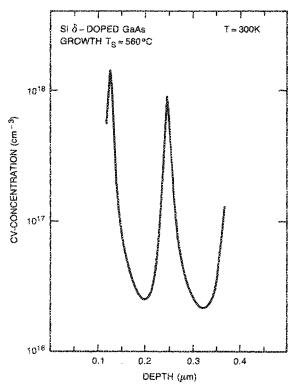

The capability of C-V profiling to probe the spatial localization of the Si  $\delta$ -doped plane is illustrated in Fig. 1, which shows a typical room-temperature C-V profile of a  $\delta$ -doped structure grown at 560 °C containing four Si-doped sheets every 1200 Å. Two sharp peaks with a maximum C-V

1578

FIG. 1. C-V profile on logarithmic scale of a GaAs epilayer with multiple Si  $\delta$ -doped planes grown at 560 °C.

concentration of  $1\times10^{18}$  cm<sup>-3</sup> and a narrow width (FWHM) of 80 Å, located at 1200 and 2400 Å below the metal-semiconductor interface, are clearly observed. Breakdown occurs at higher bias voltage before the third doped sheet is fully depleted.

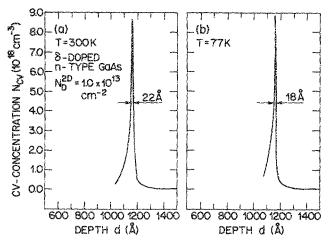

The narrowest C-V profiles are measured from samples grown at a low temperature of 500 °C. Figure 2 shows that a

FIG. 2. C-V profile measured at (a) 300 K and (b) 77 K of a Si  $\delta$ -doped structure grown at 500 °C.

very sharp peak located near 1200 Å below the Schottky contact is observed, in excellent agreement with the position of the  $\delta$ -doped sheet. A maximum C-V concentration of  $10^{19}$  cm<sup>-3</sup> is measured and the integrated C-V concentration is close to the sheet doping density of  $N_d \lesssim 1 \times 10^{13}$  cm<sup>-2</sup>. The widths of 22 Å at 300 K and 18 Å at 77 K indicate that a very high degree of localization is achieved. The narrowing of the C-V profile when the sample is cooled from 300 to 77 K is much smaller than the  $\sqrt{T}$  dependence expected from the Debye screening effect.

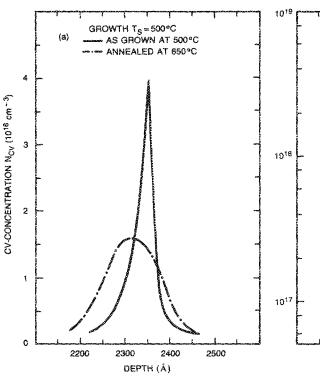

The importance of low growth temperature to achieve narrow spatial localization of Si dopants is made unambiguously clear in the following experiment. First, a structure with a  $\delta$ -doped plane 2400 Å below the surface was grown at 500 °C. Then a portion of the wafer was annealed at 650 °C in the growth chamber under As overpressure for 60 min. The C-V profiles for both samples illustrated in Fig. 3 show that

FIG. 3. C-V profiles of a Si  $\delta$ -doped GaAs grown at 500 °C and annealed subsequently at 650 °C, shown in (a) linear and (b) logarithmic scale.

J. Appl. Phys., Vol. 64, No. 3, 1 August 1988

1579

Chiu *et al.*

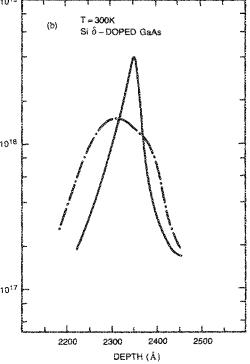

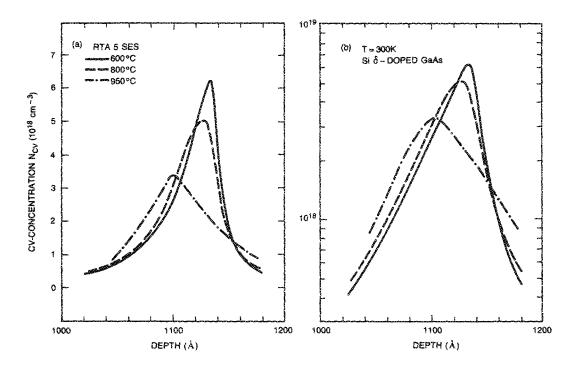

FIG. 4. Broadening of the C-V profile measured at 300 K of the sample which has a narrow width of 22 Å before the rapid thermal annealing.

the narrow width of 31 Å for the sample grown at 500 °C broadens to 143 Å after annealing. A second sample of similar structure was grown at 630 °C of which the time for the  $\delta$ doped plane maintained at the growth temperature was only 10 min. However, a much larger width of 208 Å is measured for this sample. From this finding we conclude that, in addition to Si diffusion, segregation exists at high growth temperature to give a larger C-V profile width combining both effects. Alternatively, the diffusion constant of Si impurity in the growing surface may be significantly different from that in the bulk. Unfortunately, there is no information available in either case in the temperature range of 500-600 °C. The capability of CBE to grow high-quality GaAs at low temperature to prepare extremely narrow doping plane of very high 2D impurity concentration provides an excellent way to study the diffusion phenomena in the bulk of GaAs. In particular, the  $\delta$ -doped structure is buried in the crystal which does not have other complications such as surface vacancies and the surface ambient overpressure usually encountered in conventional diffusion experiments.8 Using rapid thermal annealing (RTA), portions of the previous sample giving the narrowest C-V width of 22 Å were annealed at 600, 800, and 950 °C, respectively, for 5 s. Figure 4 shows that the C-V profile FWHMs are broadened to 35, 45, and 82 Å, respectively. Defining the difference of the halfwidths at half maximum (FWHM) as the mean penetration depth z of impurity after the annealing time t, the diffusion constant D can be obtained from  $z = 2\sqrt{(Dt/\pi)}$ . The RTA results described above give values for D of 6.6, 24, and  $140 \times 10^{-16}$  cm<sup>2</sup>/s at 600, 800, and 950 °C, respectively. Such a simple approach gives values of D in remarkable agreement to the results compiled by Greiner and Gibbons.8

More comprehensive studies of the diffusion measurements and possible diffusion mechanisms are in progress and will be discussed in a later publication.

In summary, the advantage of low growth temperature to obtain high-quality GaAs with abrupt Si doping profile has been described. C-V characterization shows extremely narrow widths of 22 and 18 Å at 300 and 77 K, respectively. Subsequent annealing experiments indicate that both diffusion and segregation of the Si dopants exist at the conventional MBE growth temperature of  $\sim 600$  °C, which will limit the ultimate control of the abruptness of doping profile. The  $\delta$ -doped structure prepared at low growth temperature is likely to provide a simple and accurate method to study the diffusion phenomena of impurities in III-V compound semiconductors.

1580 J. Appl. Phys., Vol. 64, No. 3, 1 August 1988

Chiu et al.

<sup>&</sup>lt;sup>1</sup>J. E. Cunningham, W. T. Tsang, E. F. Schubert, G. Timp, A. Chang, E. Agyekum, and J. A. Ditzenberger, J. Vac. Sci. Technol. B 6, 599 (1988); E. F. Schubert, J. E. Cunningham, W. T. Tsang, and G. L. Timp, Appl. Phys. Lett. 51, 1170 (1987).

<sup>&</sup>lt;sup>2</sup>S. Sasa, S. Muto, K. Kondo, J. Eshikawa, and S. Hiyamizu, Jpn. J. Appl. Phys. 24, L602 (1985).

<sup>&</sup>lt;sup>3</sup>T. H. Chiu, W. T. Tsang, J. E. Cunningham, and A. Robertson, Jr., J. Appl. Phys. **62**, 2302 (1987); J. Vac. Sci. Technol. B **6**, 542 (1988).

<sup>&</sup>lt;sup>4</sup>T. H. Chiu, W. T. Tsang, E. F. Schubert, and E. Agyekum, Appl. Phys. Lett. 51, 1109 (1987).

<sup>&</sup>lt;sup>5</sup>A. Robertson, T. H. Chiu, W. T. Tsang, and J. E. Cunningham (unpublished).

<sup>°</sup>W. C. Johnson and P. T. Panousis, IEEE Trans. Electron Devices ED-18, 965 (1971).

<sup>&</sup>lt;sup>7</sup>E. F. Schubert and K. Ploog, Jpn. J. Appl. Phys. 25, 966 (1986).

<sup>\*</sup>M. E. Greiner and J. R. Gibbons, J. Appl. Phys. 57, 5181 (1985).

<sup>&</sup>lt;sup>9</sup>B. L. Sharma, *Diffusion in Semiconductors* (Trans Tech Publication, Germany, 1970), p. 13.